Embedding on-chip memory allows the SoC designer to try and scale the memory wall, by customising for bandwidth, word length, etc. This approach increases bandwidth, hides latency and lowers total system power consumption by reducing off-chip memory accesses.

But implementing on-chip L3/LLC cache and on-chip main memory is also challenged by the scaling, power and cost walls.

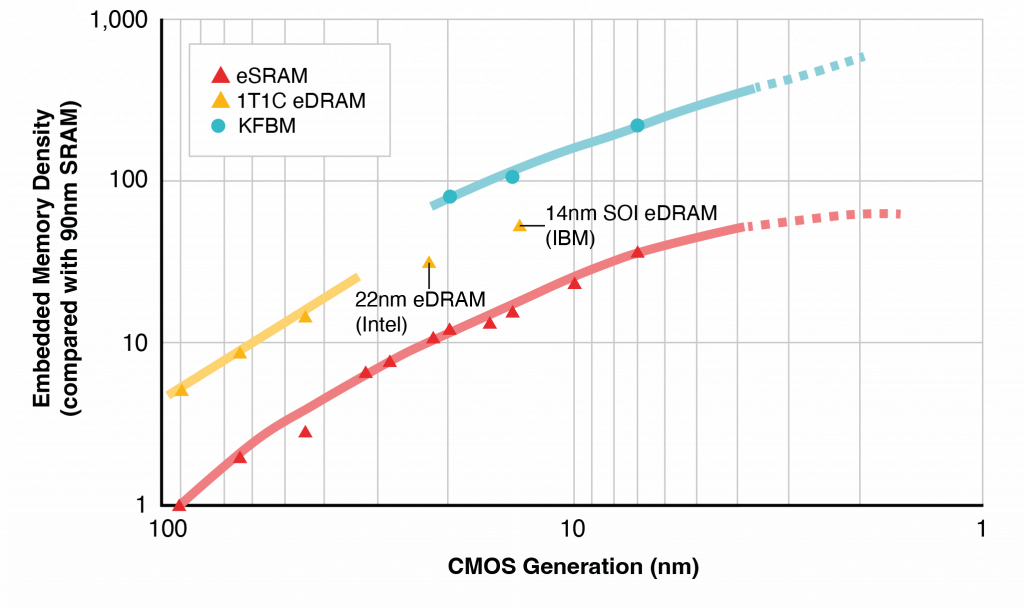

Embedded SRAM (eSRAM) does not scale as easily as logic, as transistor performance variation increases, making the SRAM unstable. Leakage current also increases, and immunity to soft errors is compromised. In fact, SRAM scaling has stalled below 7nm, threatening the opportunity to increase

SRAM capacities in the future.

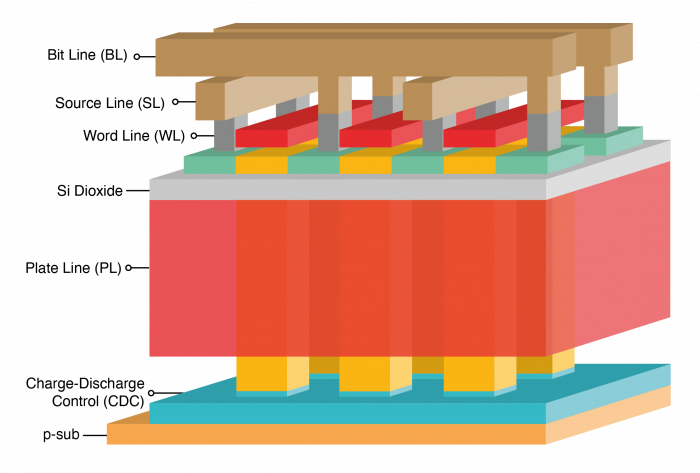

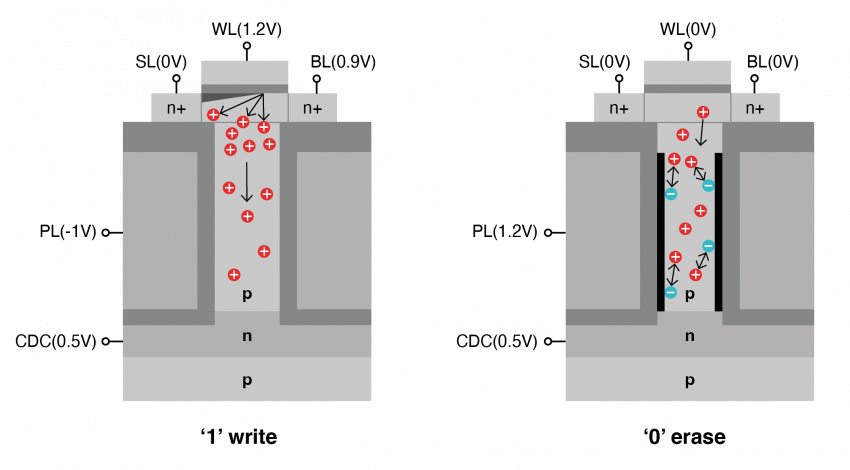

Embedded DRAM (eDRAM) theoretically offers higher density than eSRAM. But eDRAM has lower density than external DRAM, as it is implemented in a logic process (where it is offered at all). This requires additional masks and process steps, increasing cost. An additional challenge is that capacitors – which store the bit – scale badly.

Other approaches have been promoted in the market, but either require new and exotic processes and materials, or were in some way unstable in use, unable to tolerate disturbances.