Main memory is implemented in Dynamic RAM (DRAM), which provides a better trade-off between density and access times compared with Static RAM (SRAM). The density advantage of DRAM is due to its use of one transistor and one capacitor (1T1C) to store a single bit, in contrast to SRAM, which uses up to 6 transistors to store a single bit.

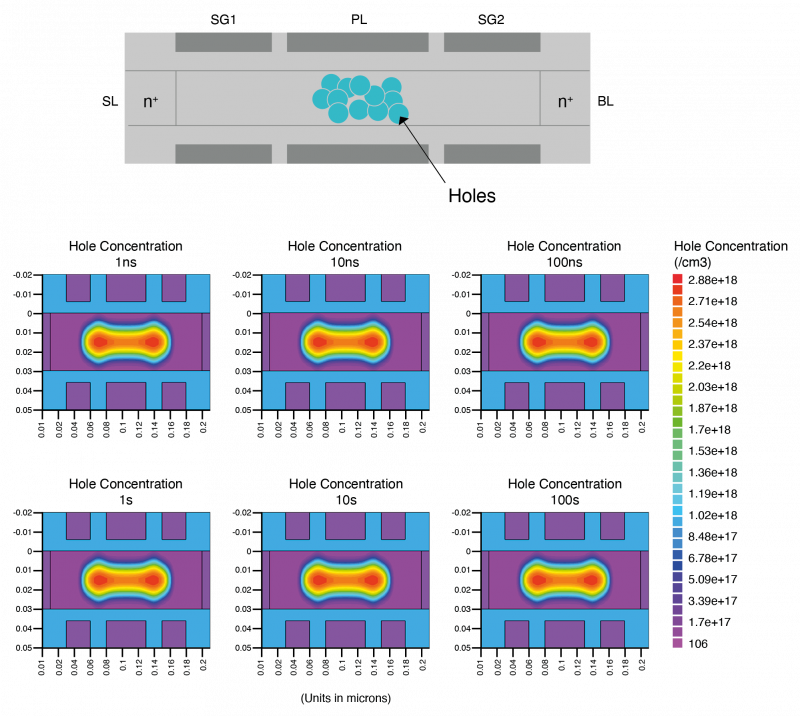

However, with the charge stored on the capacitor, reading the bit cell drains the capacitor (a destructive read), requiring the bit to be written back – and if the DRAM is not read, the charge will eventually leak out of the capacitor anyway. For this reason, DRAM bit cells must be periodically refreshed. Regular refresh cycles are power hungry and reduce read/write bandwidth.

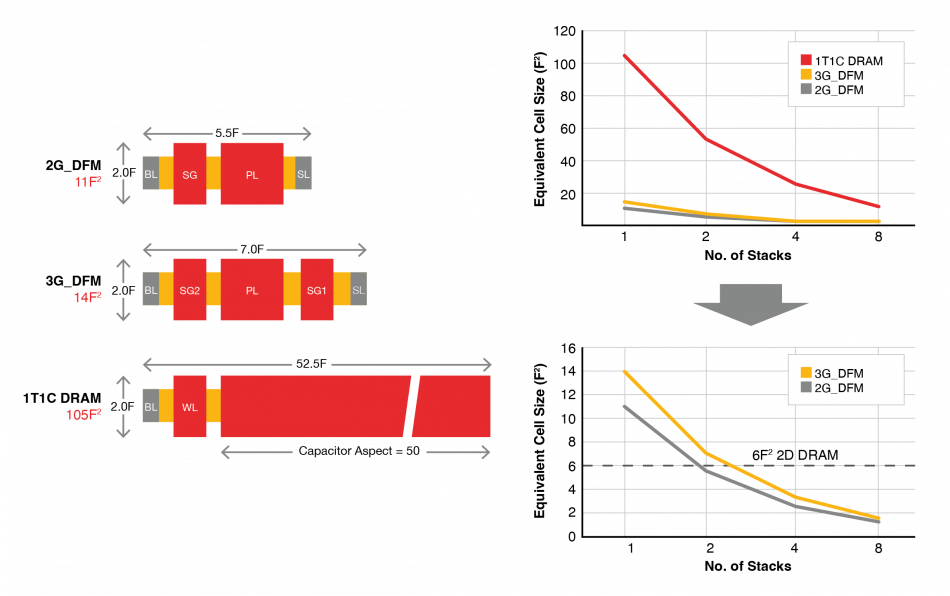

The scaling of DRAM to improve density is coming to an end, as capacitors do not shrink as well as transistors. It is difficult to build a capacitor in a small cell area with enough capacitance, leading to short data retention, insufficient sensing margin and interference. It also increases power consumption due to greater leakage currents by shortening the refresh cycle.

DRAM vendors are currently grappling with the scaling, power and cost walls while planning a transition beyond a cell size of 6F2 – dealing with both capacitor aspect ratio and capacitive coupling. Meanwhile customers demand ever-increasing amounts of external memory, while also expecting a decline in bit cost.